# SIGNAL SOURCES

# **WORD GENERATOR**

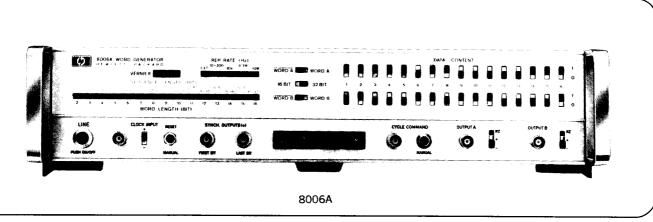

Two channel binary waveform generator Model 8006A

The 8006A generates serial digital words of variable length at clock rates up to 10 MHz. An easy selection of two 16 bit words is available. A single action puts the two 16 bit words in series to provide a 32 bit word at each output. Selectable operating modes include positive return-to-zero (RZ) format, positive and negative non-return-to-zero (NRZ) format, manual or automatic word cycling, complementary output signals, and remote programming of the data content. The remote programming feature allows conversion of parallel words to serial words. Two outputs provide trigger pulses coincident with the first and the last bit.

Additionally, a pseudo-random binary sequence variable from 7 to 65535 bits can be obtained from channel A output, with the inverted sequence available at channel B.

## **Specifications**

**Word generation:** one 4 to 32 bit word (only even number of bits) or two 2 to 16 bit words.

Word content: independently set for both words by front panel switches or remote programming (parallel data input).

Complement of each word selectable by front panel switches, WORD A - WORD A, WORD B - WORD B.

**Word cycling:** continuous or by cycle command (external trigger or manual).

Bit rate: internal, 10 Hz to 10 MHz, four ranges, continuous adjustment within ranges. Manual or external clock 0 to 10 MHz.

**Reset:** manual reset of word outputs to bit 1 in AUTO CYCLE mode and to word pause in SINGLE CYCLE mode.

**Word format:** +RZ/+NRZ/-NRZ selectable for each word output. Positive outputs have current sink capability to drive integrated circuits (TTL/DTL).

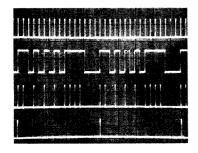

External clock

NRZ Output (16 bit continuous word recycling)

3. RZ Output signal 4. First bit synch pulse **Synch outputs:** trigger pulses corresponding to the first bit (leading edge) and last bit (trailing edge).

**Pseudo-random sequence generation PRN:** provides a linear shift register sequence at channel A output and the inverted sequence at channel B output. Maximum bit rate is 9 MHz.

**Sequence length:** variable from 7 to 65535 bits. **Trigger pulse:** selectable for each bit in sequence.

#### Interface:

#### Clock input:

**Repetition rate:** 0 to 10 MHz. Amplitude:  $>\pm2$  V,  $<\pm10$  V.

**Width:** >15 ns at  $\pm 1$  V. Input impedance: >500 $\Omega$ .

#### Cycle command input:

**Minimum period:** word length plus 100 ns. Amplitude >+2 V, <+10 V.

**Width:** >15 ns, at 1 V. Input impedance:  $>500\Omega$ .

External data inputs: no storage capability for programmed data.

**Low state:** contact closure, saturated DTL or voltage source (TTL) >0 V, <+0.8 V.

**High state:** open, off DTL or voltage source (TTL) >+2.4 V, <+5 V.

# Synch outputs:

Amplitude: >+2 V across  $50\Omega$ .

**Width:** approx. 40 ns. Output impedance:  $50\Omega$ .

### Word outputs:

**Positive NRZ, RZ:** high:  $\pm 2.5$  V across  $50\Omega$ , source impedance  $50\Omega$ . Low:  $\geq -0.3$  V,  $\leq \pm 0.3$  V, source impedance approx.  $0\Omega$ . Current sink capability 80 mA maximum.

RZ pulse width: approx. 45 ns.

**Negative NRZ:** high: 0 V. low: -5 V across  $50\Omega$ , source impedance  $50\Omega$ .

Transition times: <10 ns.

#### General

Operating temperature: 0° to 50°C.

**Power:** 115 V or 230 V  $\pm 10\%/-15\%$ , 48 Hz to 440 Hz, 59 W.

Weight: net, 131/4 lbs (6 kg).

**Dimensions:**  $16\frac{3}{4}$ " wide, 3-15/32" high,  $13\frac{1}{4}$ " deep (425,5 x 88,2 x 337 mm).

Price: Model 8006A, \$1200

Option 001: rear panel clock output. Amplitude approx. 2 V across 50Ω. Source impedance approx. 50Ω. Pulse width approx. 30 ns. Price: add \$30.